Bosch: IP core complies to LIN 1.3, 2.0, or 2.1

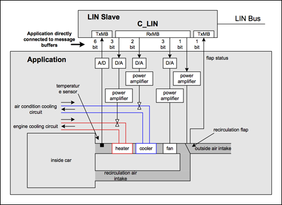

Hard-coded state machines control the LIN functions without the need of a micro-controller. Discrete Receive Message Buffer outputs directly control application blocks and (vice versa) application layer outputs could be connected directly to the discrete Transmit Message Buffer inputs. Thus the module is intended for low-cost slave solutions, explained the supplier. To meet this requirement, the user can adapt the IP core to the application by configuration. This makes it possible to avoid circuit overhead. Also during runtime many parameters can be re-configured.

The IP core supports bit-rates up to 19,2 kbit/s, when a 0,3-MHz clock with an accuracy of ±13 % is used. Sleep mode and wake-up procedures are implemented. An automatic start of the wake-up procedure on no-bus activity is supported optionally. The LIN 2.0 core requires 3900 gates, the LIN 1.3 core needs 3100 gates.